Circuitus integratus automotivus L9369-TR, impulsores portarum, ad usum specificum freni electrici stationarii.

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | STMicroelectronics |

| Categoria Producti: | Rectores Portarum |

| RoHS: | Detalia |

| Productum: | Circuiti Integrati Rectoris - Varii |

| Typus: | Latus Altum, Latus Humile |

| Modus Montandi: | SMD/SMT |

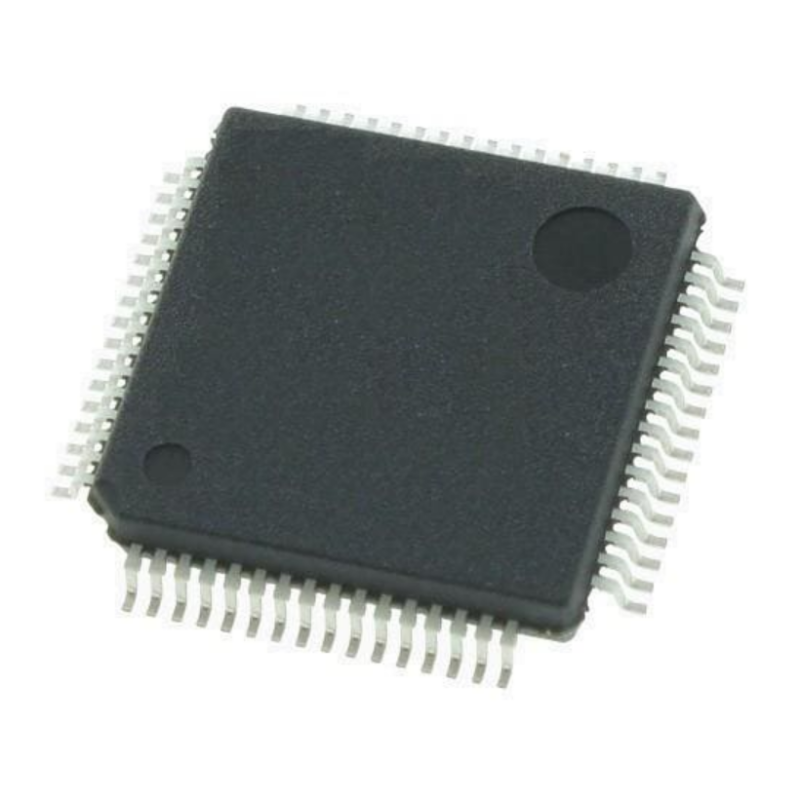

| Sarcina / Capsa: | LQFP-64 |

| Numerus Aurigarum: | 2 Auriga |

| Numerus Egressuum: | 2 Output |

| Tensio Alimentaria - Minimum: | 3.4 V |

| Tensio Alimentaria - Maxima: | 40 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 175°C |

| Series: | L9369 |

| Involucrum: | Rotula |

| Involucrum: | Taenia Seca |

| Involucrum: | MouseReel |

| Marca: | STMicroelectronics |

| Humoribus Sensibilis: | Ita |

| Typus Producti: | Rectores Portarum |

| Quantitas Sarcinae Fabricae: | mille |

| Subcategoria: | PMIC - Circuiti Integrati Administrationis Potestatis |

| Pondus Unitarium: | 0.012335 unciae |

♠ Circuitus integratus autocineticus ad usum specificum freni electrici stationarii

L9369 applicationem specificam freni electrici stationarii dirigit, aptum ad configurationem systematis in funiculo trahenti vel Unitate Motoris Redactoris (MGU).

Nuclei sunt duo stadia impulsoria pontis H ad octo FET externos pro actuatoribus frenorum rotarum posteriorum impellendos. Stadia plene impelluntur et configurantur per SPI, etiam in modo moderationis PWM et contra nimium currentem proteguntur, cum monitoribus tensionum drainsource et gate-source.

Acquisitio tensionum et currentium motorum synchronizatorum per amplificatores differentiales plenos cum amplificatione programmabili et accurata et offset humili necnon decem modulatoria sigma-delta ADC perficitur.

Duo gradus HS/LS configurabiles adsunt cum tensione egressus programmabili ad series LED impellendas, cum regulatione praeactionis.

Duae interfacies Sensoris Velocitatis Motoris (MSS) praesto sunt ad acquirendam responsum positionis ab actuatoribus freni (communicatis cum stadio impulsoris lucernae et GPIO).

Series interfacierum quattuor aciculis GPIO (General Purpose I/O) completur, et interfacies pugae permittit ut requisita specifica clientium ex consolo pugae freni electronici stationarii (EPB) tam in Modo Normali quam in Modo Somni administrentur.

Qualificatus AEC-Q100

Conceptus securitatis functionalis pro ISO26262obsequium

Quattuor prae-impulsores portae lateris superioris et inferioris pro octoNFETs potentiae externae

Protectio supercurrentis cum programmabililimina

Programmabile et ab NFET independenslimina pro monitorio VDS

Decem amplificatores plene differentiales integrati cumoffset humile, amplificatio praecisissima, et auto-probatio

Decem canales ADC separati ad digitalesProcessus currentis et tensionis motoris

mensura

32-bit – 10 MHz SPI cum CRC pro internoconfiguratio, auto-probatio et diagnostica

Plena impulsio NFETs potentiae externae usque adTensio ingressus pilae 5.5 V

Monitorium in fonte potentiae principali etBIST continuum pro regulatoribus internis

Referentia duplicis lacunae zonae

Quattuor stadia I/O Usus Generalis (GPIO)

Interfacies Button (9 paxilli I/O configurabiles) promonitorium et diagnostica in Normali etModus Somni.

Duo Sensores Velocitatis Motoris (MSS) interfaciem habentinformationes celeritatis per responsa acquirenda suntsensoria Hall externa.

Systema expergefactio in Modo Somni

Custos (per SPI configurabilis)