TPS51200QDRCRQ1 Novus et Originalis Circuitus Integratus Specializatus pro Administratione Potestatis

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Instrumenta Texana |

| Categoria Producti: | Administratio Energiae Specialisata - PMIC |

| RoHS: | Detalia |

| Series: | TPS51200-Q1 |

| Typus: | Autocinetica |

| Modus Montandi: | SMD/SMT |

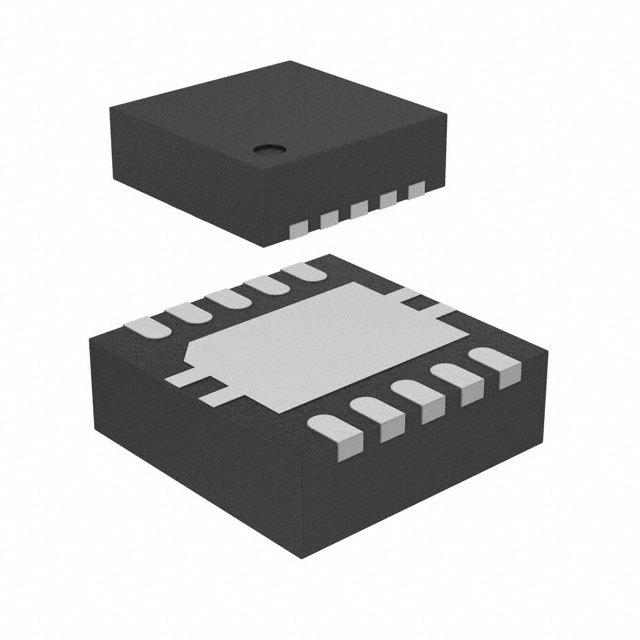

| Sarcina / Capsa: | VSON-10 |

| Currens Egressus: | 600 mA |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 125°C |

| Qualificatio: | AEC-Q100 |

| Involucrum: | Rotula |

| Involucrum: | Taenia Seca |

| Involucrum: | MouseReel |

| Marca: | Instrumenta Texana |

| Humoribus Sensibilis: | Ita |

| Cursus Operandi Subministrationis: | 700 microA |

| Pd - Dissipatio Potentiae: | 0.79 W |

| Typus Producti: | Administratio Energiae Specialisata - PMIC |

| Quantitas Sarcinae Fabricae: | tria milia |

| Subcategoria: | PMIC - Circuiti Integrati Administrationis Potestatis |

| Pondus Unitarium: | 0.001386 unciae |

♠TPS51200-Q1 Regulator Terminatorius DDR Fontis et Receptoris

Instrumentum TPS51200-Q1 est regulator terminationis duplicis frequentiae datorum (DDR) receptoris et fontis, specialiter designatus pro systematibus humilis tensionis ingressus, humilis sumptus, et parvi strepitus, ubi spatium est consideratio clavis. Instrumentum TPS51200-Q1 celerem responsionem transitoriam servat et tantum minimam capacitatem egressus 20 μF requirit. Instrumentum TPS51200-Q1 functionem sensus remoti et omnia requisita potentiae pro terminatione bus DDR, DDR2, DDR3, DDR3L, DDR3 humilis potentiae et DDR4 VTT sustinet.

Praeterea, instrumentum TPS51200-Q1 signum PGOOD cum canali aperto praebet ad regulationem exitus monitorandam et signum EN quod adhiberi potest ad VTT exonerandum per S3 (suspensio ad RAM) pro applicationibus DDR.

Instrumentum TPS51200-Q1 in involucro VSON-10 thermaliter efficiente praesto est, et aestimatum est...

et viridis et sine plumbo. Instrumentum a –40°C ad 125°C specificatur.

• Idoneus ad Usus Automotivos

• Ductio Probationis AEC-Q100 cum Sequentibus Resultatibus:

– Temperatura Instrumenti Gradus 1: –40°C ad 125°C Temperatura Operationis Ambientalis

– Classificatio ESD secundum instrumentum HBM Gradus 2

– Classificatio ESD CDM Instrumenti Gradus C4B

• Tensio Ingressa: Sustinet Rail 2.5-V et Rail 3.3-V

• VLDOIN Tensio: 1.1 V ad 3.5 V

• Regulator Terminus Fontis/Deversorii Compensationem Depressionis Includit

• Capacitas Egressus Minima 20-μF (plerumque 3 × 10-μF MLCCs) pro Applicationibus Terminationis Memoriae (DDR) requiritur.

• PGOOD ad Regulationem Productionis Monitorandam

• Input EN

• Ingressus REFIN permittit vestigationem ingressuum flexibilem sive directe sive per divisorem resistoris.

• Sensus Remotus (VOSNS)

• ±10-mA Referentia Bufferata (REFOUT)

• Initium Molle, UVLO et OCL integrata

• Clausura Thermalis

• Specificationibus DDR et DDR2 JEDEC obtemperat; Applicationes DDR3, DDR3L, DDR3 Parvae Potentiae et DDR4 VTT sustinet.

• Sarcina VSON-10 cum Pulvino Thermali Exposito

• Regulator Terminationis Memoriae pro DDR, DDR2, DDR3, DDR3L, DDR3 Parvae Potentiae et DDR4

• Computatrum portabile, Computatrum desktop, Servus

• Telecommunicatio et Communicationes Datarum, Statio Basis GSM, Televisorium LCD et Televisorium PDP, Copiator et Impressor, Arca Decoder