Microprocessores P1020NXN2HFB – MPU 800/400/667 ET NE r1.1

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | NXP |

| Categoria Producti: | Microprocessores - MPU |

| RoHS: | Detalia |

| Modus Montandi: | SMD/SMT |

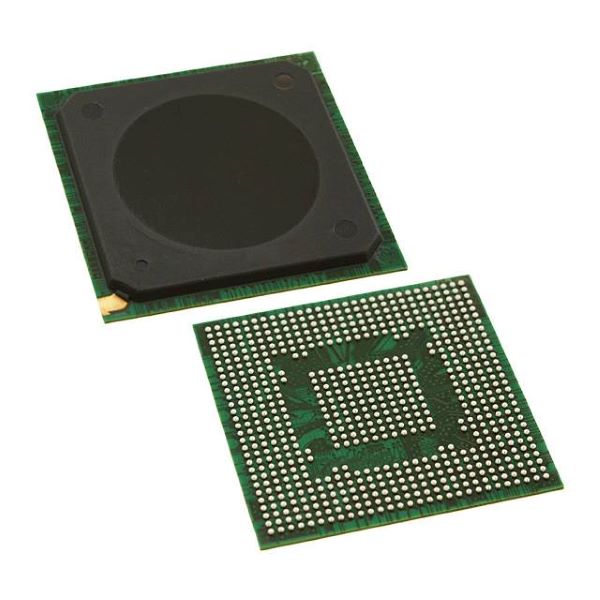

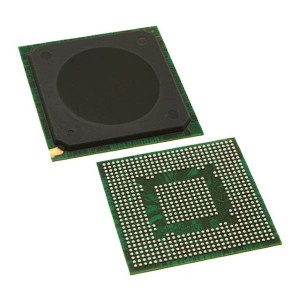

| Sarcina/Capsa: | TEPBGA-689 |

| Series: | P1020 |

| Nucleus: | e500 |

| Numerus Nucleorum: | Duo Nuclei |

| Latitudo Bus Datorum: | Triginta duo bit |

| Frequentia Horologii Maxima: | 800 MHz |

| Memoria Instructionum Cache L1: | 2 x 32 kB |

| Memoria Datorum Cessandi L1: | 2 x 32 kB |

| Tensio Alimentationis Operativae: | 1 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 125°C |

| Involucrum: | Ferculum |

| Marca: | NXP Semiconductors |

| Tensio I/O: | 1.5 V, 1.8 V, 2.5 V, 3.3 V |

| Typus Instructionis: | Punctum Fluitans |

| Typus Interfaciei: | Aethernet, I2C, PCIe, SPI, UART, USB |

| Instructio / Memoria Datorum Cache L2: | 256 kB |

| Genus Memoriae: | L1/L2 Celula |

| Humoribus Sensibilis: | Ita |

| Numerus I/O: | XVI I/O |

| Series Processoris: | QorIQ |

| Typus Producti: | Microprocessores - MPU |

| Quantitas Sarcinae Fabricae: | 27 |

| Subcategoria: | Microprocessores - MPU |

| Nomen Mercatorium: | QorIQ |

| Tempora Custodiae: | Nullum Temporis Custodis |

| Alias Partium #: | 935310441557 |

| Pondus Unitarium: | 5.247 grammata |

• Duo nuclei 32-bit summae efficacitatis, in technologia Power Architecture® constructi:

– inscriptionem physicam 36-bit

– Sustentatio puncti fluitantis duplicis praecisionis

– cella instructionum L1 32 Kbyte et cella datorum L1 32 Kbyte pro quolibet nucleo

– Frequentia horologii 533 MHz ad 800 MHz

• Memoria celata L2 256 Kbyte cum ECC. Etiam configurabilis ut memoria SRAM et reconditoria.

• Tres moderatores Ethernet trium celeritatum amplificati 10/100/1000 Mbps (eTSECs)

– Acceleratio TCP/IP, qualitas servitii, et facultates classificationis

– Auxilium IEEE® 1588

– Imperium fluxus sine damno

– MII, RMII, RGMII, SGMII

• Interfacies celeres varias optiones multiplexationis sustinentes:

– Quattuor SerDes usque ad 2.5 GHz/via per moderatores multiplexatae

– Duae interfacies PCI Express

– Duae interfacies SGMII

• Moderator USB celeritatis altae (USB 2.0)

– Auxilium hospitis et machinae

– Interfacies moderatoris hospitis amplificata (EHCI)

– Interfacies ULPI ad PHY

• Moderator digitalis securus amplificatus (SD/MMC)

• Interfacies peripherica serialis amplificata (eSPI)

• Machina securitatis integrata

– Protocolla sustentata comprehendunt ARC4, 3DES, AES, RSA/ECC, RNG, SSL/TLS unius transitus.

– Acceleratio XOR

• Moderator memoriae SDRAM DDR2/DDR3 32-bit cum auxilio ECC

• Moderator interruptionis programmabilis (PIC) cum norma OpenPIC congruens

• Unus moderator DMA quattuor canalum

• Duo moderatores I2C, DUART, temporaria

• Moderator localis bus amplificatus (eLBC)

• TDM

• 16 signa I/O generalis usus

• Temperaturae iuncturae operativae (Tj): 0–125°C et –40°C ad 125°C (specificatio industrialis)

• WB-TePBGA II 31 × 31 mm, 689-clavorum (BGA plastica cum nexu filorum, temperatura aucta)