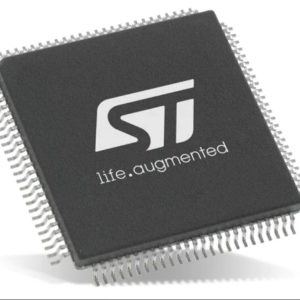

SPC563M64L5COAR Microcontrollores 32-bit – MCU 32-BIT MCU Inclusus 80 MHz, 1.5 Mbyte

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | STMicroelectronics |

| Categoria Producti: | Microcontrollores 32-bit - MCU |

| RoHS: | Detalia |

| Series: | SPC563M64L5 |

| Modus Montandi: | SMD/SMT |

| Sarcina/Capsa: | LQFP-144 |

| Nucleus: | e200z335 |

| Magnitudo Memoriae Programmatis: | 1.5 MB |

| Magnitudo Memoriae Memoriae Datorum: | 94 kB |

| Latitudo Bus Datorum: | Triginta duo bit |

| Resolutio ADC: | Duo x octo bit/decem bit/duodecim bit |

| Frequentia Horologii Maxima: | 80 MHz |

| Numerus I/O: | 105 I/O |

| Tensio Alimentaria - Minimum: | 5 V |

| Tensio Alimentaria - Maxima: | 5 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 125°C |

| Qualificatio: | AEC-Q100 |

| Involucrum: | Rotula |

| Involucrum: | Taenia Seca |

| Involucrum: | MouseReel |

| Marca: | STMicroelectronics |

| Humoribus Sensibilis: | Ita |

| Typus Producti: | Microcontrollores 32-bit - MCU |

| Quantitas Sarcinae Fabricae: | quingenti |

| Subcategoria: | Microcontrollores - MCU |

| Pondus Unitarium: | 1.290 grammata |

♠ Microcontrollore (MCU) 32-bit in Architectura Potentiae® fundato ad applicationes potentiae autocineticae

Hi microcontrollores autocinetici 32-bit familia machinarum System-on-Chip (SoC) sunt, quae multas novas functiones una cum technologia CMOS 90 nm altae efficaciae continent, ut substantialem reductionem sumptus per functionem et significantem augmentum efficaciae praebeant. Nucleus processoris hospitis provectus et sumptibus efficax huius familiae moderatorum autocineticorum in technologia Power Architecture® constructus est. Haec familia emendationes continet quae aptitudinem architecturae in applicationibus inclusis amplificant, auxilium instructionum additum pro Processu Signorum Digitalium (DSP) includit, technologias integrat — ut unitatem processoris temporis amplificatam, convertorem analogum-digitalem in ordinem amplificatum, Retem Areae Moderatorum, et systema modulare input-output amplificatum — quae magni momenti sunt pro applicationibus motorum hodiernis inferioris ordinis. Machina unum gradum hierarchiae memoriae habet, constantem usque ad 94 KB SRAM in chip et usque ad 1.5 MB memoriae flash internae. Machina etiam Interfaciem Bus Externam (EBI) ad 'calibrationem' habet.

■ Nucleus CPU e200z335, exemplar singulare, Architecturae Potentiae 32-bit, cum Libro E congruens

– Incrementa Codificationis Longitudinis Variabilis (VLE) ad magnitudinem codicis reducendam includit.

■ Moderator Accessus Memoriae Directi (DMA) 32-canalis

■ Moderator Interruptionum (INTC) capax tractandi 364 fontes interruptionum prioritatis selectabilis: 191 fontes interruptionum periphericarum, 8 interruptiones programmatum et 165 interruptiones reservatas.

■ Ansa Phase-Locked Frequency-Modulated (FMPLL)

■ Calibratio Interfacies Bus Externae (EBI)(a)

■ Unitas Integrationis Systematis (SIU)

■ Usque ad 1.5 Mbyte memoria Flash in chip cum moderatore Flash

– Accelerator acquisitionis ad accessum Flash unius cycli @80 MHz

■ Memoria RAM statica in chip usque ad 94 Kbyte (inclusa usque ad 32 Kbyte memoria RAM subsidiaria)

■ Modulus Adiutorius Initiationis (BAM)

■ Unitas Processoria Temporis (eTPU) amplificata secundae generationis 32 canalium

– 32 canales eTPU ordinarii

– Emendationes architecturae ad efficientiam codicis augendam et flexibilitatem augendam

■ Systema Modulare Input-Output (eMIOS) sedecim canalibus amplificatum

■ Conversor Analogicus-Digitalis Ordinis Augmentatus (eQADC)

■ Filtrum decimationis (pars eQADC)

■ Sensor temperaturae matricis siliconis

■ Duo moduli Interfaciei Periphericae Serialis Deserialis (DSPI) (compatibiles cum Microsecond Bus)

■ Duo moduli Interfaciei Communicationis Serialis (eSCI) amplificati, cum LIN congruentes

■ Duo moduli Retis Areae Moderatoris (FlexCAN) qui CAN 2.0B sustinent

■ Regulator Portus Nexus (NPC) secundum normam IEEE-ISTO 5001-2003

■ IEEE 1149.1 (JTAG) subsidium

■ Interfacies Nexus

■ Regulator tensionis in chip integratus qui copias internas 1.2 V et 3.3 V ex fonte externo 5 V praebet.

■ Designatum pro LQFP144 et LQFP176