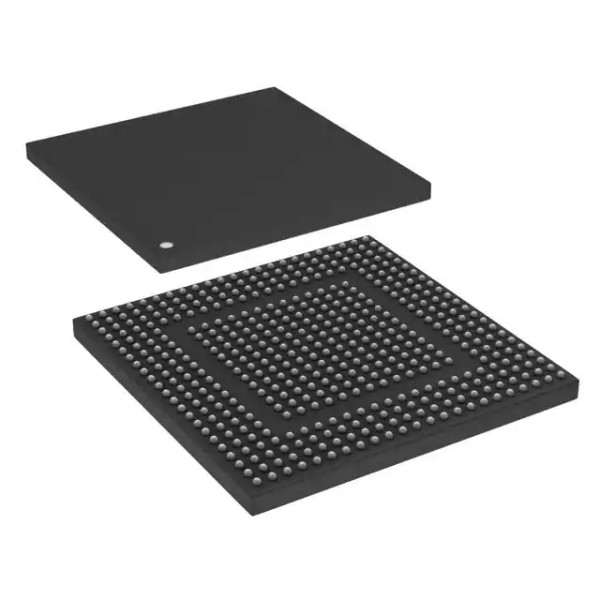

SPC5675KFF0MMS2 Microcontrollores 32-bit MCU 2MFlash 512KSRAM EBI

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | NXP |

| Categoria Producti: | Microcontrollores 32-bit - MCU |

| RoHS: | Detalia |

| Series: | MPC5675K |

| Modus Montandi: | SMD/SMT |

| Sarcina / Capsa: | BGA-473 |

| Nucleus: | e200z7d |

| Magnitudo Memoriae Programmatis: | 2 MB |

| Magnitudo Memoriae Memoriae Datorum: | 512 kB |

| Latitudo Bus Datorum: | Triginta duo bit |

| Resolutio ADC: | Duodecim bit |

| Frequentia Horologii Maxima: | 180 MHz |

| Tensio Alimentaria - Minimum: | 1.8 V |

| Tensio Alimentaria - Maxima: | 3.3 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 125°C |

| Qualificatio: | AEC-Q100 |

| Involucrum: | Ferculum |

| Tensio Alimentationis Analogica: | 3.3 V/5 V |

| Marca: | NXP Semiconductors |

| Typus RAM datorum: | SRAM |

| Tensio I/O: | 3.3 V |

| Humoribus Sensibilis: | Ita |

| Series Processoris: | MPC567xK |

| Productum: | MCU |

| Typus Producti: | Microcontrollores 32-bit - MCU |

| Genus Memoriae Programmatis: | Fulgur |

| Quantitas Sarcinae Fabricae: | 420 |

| Subcategoria: | Microcontrollores - MCU |

| Tempora Custodiae: | Custodis Temporis |

| Alias Partium #: | 935310927557 |

| Pondus Unitarium: | 0.057260 unciae |

♠ Microcontrollor MPC5675K

Microcontroller MPC5675K, solutio SafeAssure, est...Moderator inclusus 32-bit ad rectores provectos designatusSystemata adiutoria cum RADAR, imaginibus CMOS, LIDARet sensoria ultrasonica, et multiplices moderationes motorum triphasiumapplicationes ut in vehiculis hybridis electricis (HEV) inApplicationes autocineticae et industriales altae temperaturae.

Sodalis familiae MPC5500/5600 societatis NXP Semiconductor,Architecturam Potestatis Libro E congruentem continet.nucleus technologicus cum Codificatione Longitudinis Variabilis (VLE). HocNucleus cum Architectura Potentiae inclusa congruitcategoriae, et modus usoris centum centesimis compatibilis est cumArchitectura instructionum usoris (UISA) originalis Power PC™.Praebet efficacitatem systematis usque ad quadruplicem maiorem quam eius.Decessor MPC5561, dum tibi firmitatem etfamiliaritas technologiae Architecturae Potentiae probatae.

Series completa apparatuum et programmatumInstrumenta progressionis praesto sunt ad simplificandum et accelerandumdesignatio systematis. Auxilium progressionis praesto est abpraecipui venditores instrumentorum compilatores, debugatores et praebentesAmbitus evolutionis simulationis.

• Nucleus duplex e200z7d summae efficacitatis

— Technologia Architecturae Potestatis 32-bit CPU

— Frequentia interna usque ad 180 MHz

— Nucleus duplex

— Codificatio longitudinis variabilis (VLE)

— Unitas administrationis memoriae (MMU) cum 64 inscriptionibus

— cella instructionum 16 KB et cella datorum 16 KB

• Memoria praesto

— Memoria flash codicis usque ad 2 MB cum ECC

— Memoria fulgurans datorum 64 KB cum ECC

— Usque ad 512 KB SRAM in chip cum ECC

• Ratio securitatis nova SIL3/ASILD: modus LockStep et praesidium contra errores

— Sphaera replicationis (SoR) pro componentibus principalibus

— Unitates redundantiae probandae in exitibus SoR cum FCCU connexis

— Unitas colligendi et moderandi errores (FCCU)

— Auto-examinatio memoriae (MBIST) et logicae (LBIST) tempore initii, ab apparatu incitata, intrinsecus facta.

— Auto-probatio tempore initii inclusa pro ADC et memoria flash

— Temporis custos securitatis auctus replicatus

— Sensor temperaturae substrati siliconici (matricem)

— Interruptio non-occultabilis (NMI)

— Unitas tutelae memoriae sedecim regionum (MPU)

— Unitates monitoriae horologii (CMU)

— Unitas administrationis potentiae (PMU)

— Unitates redundantiae cyclicae (CRC)

• Modus Parallelus Separatus ad usum nucleorum replicatorum magnae efficaciae

• Nexus Classis 3+ interfacies

• Interruptiones

— Moderator interruptionis sedecim prioritatis replicatus

• GPIOs singillatim programmabiles ut ingressum, exitum, vel functionem specialem

• Tres unitates eTimer usus generalis (sex canales singulae)

• Tres unitates FlexPWM cum quattuor canalibus 16-bit per modulum

• Interfacies communicationis

— quattuor moduli LINFlex

— Tres moduli DSPI cum generatione automatica selectionis microplagulae

— 4 interfacies FlexCAN (2.0B Activae) cum 32 obiectis nuntiorum

— Modulus FlexRay (V2.1) cum canali duplici, usque ad 128 obiecta nuntiorum et usque ad 10 Mbit/s

— Moderator Aetherneticus Celeris (FEC)

— 3 I2Moduli C

• Quattuor conversores analogico-digitales (ADC) 12-bit

— XXII canales ingressus

— Unitas programmabilis impulsus transversalis (CTU) ad synchronizandum conversionem ADC cum temporizatore et PWM

• Interfacies bus externa

• Moderator memoriae DDR externus 16-bit

• Interfacies digitalis parallela (PDI)

• Programma initiale CAN/UART in chip integratum

• Operari potest cum unica tensione 3.3 V

— Moduli 3.3 V tantum: I/O, oscillatores, memoria flash

— Moduli 3.3 V vel 5 V: ADC, alimentatione ad VREG internum

— 1.8–3.3 V fasciculus copiae: DRAM/PDI

• Temperaturae iuncturae operativae –40 ad 150°C