STM32F105RCT6 Microcontrollores ARM – MCU 32BIT Cortex 64/25 LINEA CONNECTIVITAS M3

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | STMicroelectronics |

| Categoria Producti: | Microcontrollores ARM - MCU |

| RoHS: | Detalia |

| Series: | STM32F105RC |

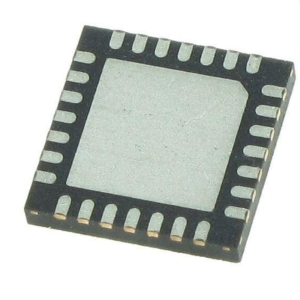

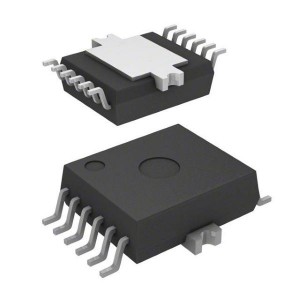

| Modus Montandi: | SMD/SMT |

| Sarcina / Capsa: | LQFP-64 |

| Nucleus: | ARM Cortex M3 |

| Magnitudo Memoriae Programmatis: | 256 kB |

| Latitudo Bus Datorum: | Triginta duo bit |

| Resolutio ADC: | Duodecim bit |

| Frequentia Horologii Maxima: | 72 MHz |

| Numerus I/O: | 51 I/O |

| Magnitudo Memoriae Memoriae Datorum: | 64 kB |

| Tensio Alimentaria - Minimum: | Duo voltia |

| Tensio Alimentaria - Maxima: | 3.6 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | +85°C |

| Involucrum: | Ferculum |

| Marca: | STMicroelectronics |

| Typus RAM datorum: | SRAM |

| Altitudo: | 1.4 mm |

| Typus Interfaciei: | CAN, I2C, SPI, USART |

| Longitudo: | Decem millimetra |

| Humoribus Sensibilis: | Ita |

| Numerus Canalium ADC: | Canalis XVI |

| Numerus Temporatorum/Numeratorum: | Decem Temporatores |

| Series Processoris: | ARM Cortex M |

| Typus Producti: | Microcontrollores ARM - MCU |

| Genus Memoriae Programmatis: | Fulgur |

| Quantitas Sarcinae Fabricae: | 960 |

| Subcategoria: | Microcontrollores - MCU |

| Nomen Mercatorium: | STM32 |

| Latitudo: | Decem millimetra |

| Pondus Unitarium: | 0.012088 unciae |

♠ Linea connectivitatis, MCU 32-bit in ARM® fundatum cum memoria Flash 64/256 KB, USB OTG, Ethernet, 10 temporatores, 2 CAN, 2 ADC, 14 interfacies communicationis

Familia linearum connectivitatis STM32F105xx et STM32F107xx nucleum RISC ARM® Cortex®-M3 32-bit summae efficacitatis, frequentia 72 MHz operantem, memorias inclusas celerrimas (memoria Flash usque ad 256 Kbytes et SRAM 64 Kbytes), et amplam seriem input/output amplificatorum et periphericorum duobus busibus APB connexorum comprehendit. Omnia instrumenta duos convertitores analogico-digitales 12-bit, quattuor temporatores generales 16-bit, una cum temporatore PWM, necnon interfaces communicationis normales et provectas offerunt: usque ad duos I2C, tres SPI, duos I2S, quinque USART, systema FS USB OTG et duos CAN. Ethernet in STM32F107xx tantum praesto est.

Familia linearum connectivitatis STM32F105xx et STM32F107xx operatur in ambitu temperaturae inter –40 et +105°C, a fonte potentiae 2.0 ad 3.6 V. Series completa modorum conservationis potentiae permittit designationem applicationum parvae potentiae.

Familia linearum connectivitatis STM32F105xx et STM32F107xx instrumenta in tribus diversis generibus involucri offert: a 64 pinis ad 100 pinis. Pro instrumento electo, variae series periphericarum includuntur; descriptio infra conspectum praebet totius seriei periphericarum in hac familia propositarum.

Hae proprietates familiam microcontrollorum lineae connectivitatis STM32F105xx et STM32F107xx aptam reddunt ad amplam applicationum varietatem, ut puta impulsiones motorum et imperium applicationum, apparatum medicum et manuale, applicationes industriales, PLCs, inverteres, impressores, et lectores automaticos, systemata alarmis, intercom video, HVAC et apparatum audio domesticum.

• Nucleus: CPU ARM® Cortex®-M3 32-bit

– Frequentia maxima 72 MHz, effectus 1.25 DMIPS/MHz (Dhrystone 2.1) in statu exspectationis 0 accessus memoriae

– Multiplicatio unius cycli et divisio instrumentorum

• Memoriae

– 64 ad 256 Kbytes memoriae Flash

– 64 Kbytes SRAM usus generalis

• Horologium, reinitializatio et administratio copiarum

– 2.0 ad 3.6 V alimentationis applicationis et I/O

– POR, PDR, et detector tensionis programmabilis (PVD)

– Oscillator crystallinus 3-ad-25 MHz

– RC interna 8 MHz ab officina praeparata

– RC interna 40 kHz cum calibratione

– Oscillator 32 kHz pro RTC cum calibratione

• Potentia humilis

– Modi Somni, Sistendi et Exspectandi

– Copia VBAT pro RTC et registris subsidiariis

• Conversores A/D 2 × 12-bit, 1 µs (16 canales)

– Ambitus conversionis: 0 ad 3.6 V

– Facultas exemplificandi et tenendi

– Sensor temperaturae

– usque ad 2 MSPS in modo interfoliato

• Duo convertores D/A duodecim bit

• DMA: moderator DMA duodecim canalium

– Peripherica sustentata: tempora, ADC, DAC, I2S, SPI, I2C et USART

• Modus depurationis

– Interfacies debug filorum serialium (SWD) et JTAG

–Cortex®-M3 Macrocellula Vestigii Inclusa™

• Usque ad 80 portas I/O celeres

– 51/80 I/O, omnes mappabiles in 16 vectoribus interruptionis externis et fere omnes tolerantes 5 V

• Unitas computationis CRC, identificatio unica 96-bit

• Usque ad decem tempora cum facultate remappationis pinout

– Usque ad quattuor temporaria 16-bit, singula cum usque ad quattuor IC/OC/PWM vel numeratore impulsuum et input encoder quadraturae (incrementalis)

– 1 × temporarium PWM moderationis motoris 16-bit cum generatione temporis mortui et sistendo in casu necessitatis

– 2 × tempora custodum (Independentia et Fenestra)

– Temporator SysTick: numerator deorsum 24-bit

– 2 × tempora fundamentalia 16-bit ad DAC impellendum

• Usque ad quattuordecim interfacies communicationis cum facultate remappationis pinout

– Usque ad 2 × interfacies I2C (SMBus/PMBus)

– Usque ad quinque USART (interfacies ISO 7816, LIN, facultas IrDA, imperium modemi)

– Usque ad 3 SPIs (18 Mbit/s), 2 cum interfacie I2S multiplexata quae accuratiam classis audio per schemata PLL provecta praebet.

– 2 × interfacies CAN (2.0B Activae) cum 512 octetis SRAM dedicatae

– Moderator USB 2.0 plenae celeritatis instrumenti/hospitis/OTG cum PHY in chip qui HNP/SRP/ID sustinet cum 1.25 Kbytis SRAM dedicatae

– MAC Ethernet 10/100 cum DMA et SRAM dedicatis (4 Kbytes): subsidium ferramentorum IEEE1588, MII/RMII in omnibus fasciculis praesto.