TPS51604DSGR Rectores Portae Synchronizationis Reductoris FET DVR

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Instrumenta Texana |

| Categoria Producti: | Rectores Portarum |

| RoHS: | Detalia |

| Productum: | Rectores Semi-Pontis |

| Typus: | Latus Altum, Latus Humile |

| Modus Montandi: | SMD/SMT |

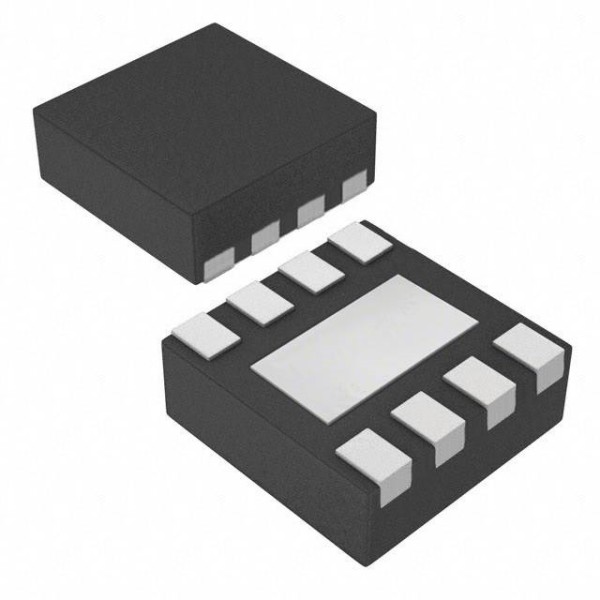

| Sarcina / Capsa: | WSON-8 |

| Numerus Aurigarum: | 2 Auriga |

| Numerus Egressuum: | 2 Output |

| Currens Egressus: | 4 A |

| Tensio Alimentaria - Minimum: | 4.5 V |

| Tensio Alimentaria - Maxima: | 5.5 V |

| Tempus Ortus: | XV ns |

| Tempus Autumnale: | Decem ns |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 105°C |

| Series: | TPS51604 |

| Involucrum: | Rotula |

| Involucrum: | Taenia Seca |

| Involucrum: | MouseReel |

| Marca: | Instrumenta Texana |

| Proprietates: | Imperium Temporis Mortui, Rectificatio Synchrona |

| Humoribus Sensibilis: | Ita |

| Cursus Operandi Subministrationis: | 600 microA |

| Tensio Alimentationis Operativae: | 4.5 V ad 28 V |

| Tensio Egressus: | 34 V |

| Typus Producti: | Rectores Portarum |

| Quantitas Sarcinae Fabricae: | tria milia |

| Subcategoria: | PMIC - Circuiti Integrati Administrationis Potestatis |

| Technologia: | Si |

| Pondus Unitarium: | 0.000384 unciae |

♠ TPS51604 Synchronus Buck FET Impulsor ad Potentiam Nuclei CPU Altae Frequentiae

Rectores TPS51604 ad applicationes VCORE CPU altae frequentiae optimizati sunt. Proprietates provectiores, ut tempus mortuum reductum et transitus automaticus ad zero, adhibentur ad efficientiam per totum ambitum oneris optimizandam.

Clavus SKIP optionem operationis CCM praebet ad moderandam tensionem emissariam sustinendam. Praeterea, TPS51604 duos modos parvae potentiae sustinet. Cum input PWM in statu tripartito, fluxus quiescens ad 130 µA reducitur, cum responso immediato. Cum SKIP in statu tripartito tenetur, fluxus ad 8 µA reducitur (plerumque 20 µs requiritur ad commutationem resumendam). Cum moderatore TI idoneo coniuncti, impulsores systema fontis potentiae praebent efficaciam exceptionalem.

Instrumentum TPS51604 in involucro WSON 2 mm x 2 mm, 8-pin, thermopolio aucto, spatium conservante inclusum est, et a –40°C ad 105°C operatur.

• Circuitus Impulsionis Temporis Mortui Reductus ad CCM Optimizatum

• Detectio Automatica Transitus Zero ad Efficientiam DCM Optimizatam

• Modi Parvae Potentiae Plures ad Efficientiam Levis Oneris Optimizatam

• Morae Viae Signalis Optimizatae ad Operationem Altae Frequentiae

• Robur Impulsoris Commutatoris BST Integrati, Optimizatum pro FET Ultrabook

• Ad impulsum FET 5-V accommodatum

• Ambitus Tensionis Ingressae Conversionis (VIN): 4.5 ad 28 V

• Fasciculus Pulvinorum Thermalium WSON, 2 mm × 2 mm, 8-clavorum

• Tabulae Computatra Centralia Processoria Altae Frequentiae cum Sequenti Potentia Ingressa Utentes:

– Adaptor

– Accumulator

– NVDC

– Ferriviae 5-V vel 12-V