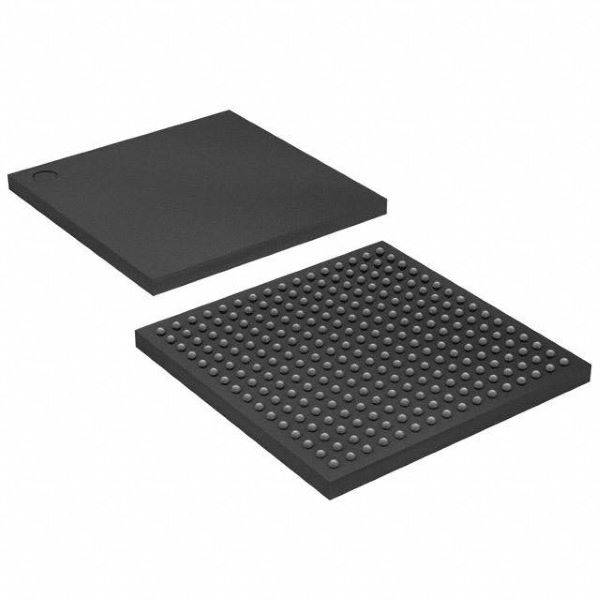

XC6SLX25-2FTG256C FPGA – Series Portarum Programmabiles in Campo Fabrica in praesenti ordines huius producti non accipit.

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Xilinx |

| Categoria Producti: | FPGA - Series Portarum Programmabiles in Campo |

| RoHS: | Detalia |

| Series: | XC6SLX25 |

| Numerus Elementorum Logicorum: | 24051 LE |

| Numerus I/O: | 186 I/O |

| Tensio Alimentaria - Minimum: | 1.14 V |

| Tensio Alimentaria - Maxima: | 1.26 V |

| Temperatura Operativa Minima: | 0°C |

| Temperatura Maxima Operativa: | +85°C |

| Frequentia Datorum: | - |

| Numerus Transceptorum: | - |

| Modus Montandi: | SMD/SMT |

| Sarcina/Capsa: | FBGA-256 |

| Marca: | Xilinx |

| Memoria RAM distributa: | 229 kbit |

| Memoria RAM Integrata - EBR: | 936 kbit |

| Frequentia Operativa Maxima: | 1080 MHz |

| Humoribus Sensibilis: | Ita |

| Numerus Sectorum Ordines Logici - LAB: | Laboratorium anni MDCCCLXXIX |

| Tensio Alimentationis Operativae: | 1.2 V |

| Typus Producti: | FPGA - Series Portarum Programmabiles in Campo |

| Quantitas Sarcinae Fabricae: | 1 |

| Subcategoria: | Circuiti Integrati Logicae Programmabiles |

| Nomen Mercatorium: | Spartanus |

| Pondus Unitarium: | 21.576 grammata |

♠ Conspectus Familiae Spartan-6

Familia Spartan®-6 facultates integrationis systematum praebet praestantissimas cum minimo sumptu totali pro applicationibus magni voluminis. Familia tredecim membrorum densitates ampliatas praebet, a 3840 ad 147443 cellulas logicas, cum dimidia parte consumptionis potentiae familiarum Spartan priorum, et connectivitate velociori et ampliore. Constructa in technologia matura processus cupri 45 nm parvae potentiae quae aequilibrium optimum sumptus, potentiae, et effectus praebet, familia Spartan-6 offert novam logicam tabulae consultationis (LUT) 6-ingressus cum duobus registris et divitiis selectis segmentorum systematis inclusis. Haec includunt RAM segmentorum 18 Kb (2 x 9 Kb), segmenta DSP48A1 secundae generationis, moderatores memoriae SDRAM, segmenta administrationis horologii modi mixti amplificata, technologiam SelectIO™, segmenta transceptoris serialis celeris potentia optimizata, segmenta Endpoint compatibilia cum PCI Express®, modos administrationis potentiae systematis provectos, optiones configurationis auto-detectionis, et securitatem IP amplificatam cum protectione AES et Device DNA. Hae proprietates alternativam programmabilem sumptu minore praebent productis ASIC consuetudinariis cum facilitate usus inaudita. FPGA Spartan-6 optimam solutionem offerunt pro designis logicis magni voluminis, designis DSP clientibus accommodatis, et applicationibus inclusis sumptu sensibilibus. FPGA Spartan-6 sunt fundamentum silicii programmabile pro suggestis designandi destinatis quae componentes programmatum et ferramentorum integratos praebent quae designatoribus permittunt ut in innovatione se concentrent simulac cyclus eorum evolutionis incipit.

• Familia Spartan-6:

• Spartan-6 LX FPGA: Logica optimizata

• Spartan-6 LXT FPGA: Conexio serialis celerrima

• Ad sumptum vile designatum

• Plures efficaces bloci integrati

• Selectio optima normarum I/O

• Pulvinariae vacillantes

• Sarcinae plasticae magnae voluminis filo coniunctae

• Potentia statica et dynamica humilis

• Processus 45 nm ad sumptum et vim electricam parvam optimus

• Modus hibernationis potentiae excludendae ad nullam potentiam

• Modus suspensus statum et configurationem cum excitatione multi-clavi et amplificatione moderationis conservat.

• Tensio interna minoris potentiae 1.0V (LX FPGAs, -1L tantum)

• Tensio interna 1.2V summae efficacitatis (FPGA LX et LXT, gradus celeritatis -2, -3, et -3N)

• Interfacies SelectIO™ multi-tensionis et multi-normae

• Usque ad 1080 Mb/s celeritas translationis datorum per differentiale I/O

• Impulsus egressus eligendus, usque ad 24 mA per aciculum

• 3.3V ad 1.2VI/O normae et protocolla

• Interfacies memoriae HSTL et SSTL pretii minoris

• Obsequentia permutationis calidae

• Frequentiae mutationis I/O adaptabiles ad integritatem signalis emendandam

• Transceptores seriales GTP celeres in FPGA LXT

• Usque ad 3.2 Gb/s

• Interfacies celerrimae, inter quas: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort, et XAUI

• Punctum terminale integratum pro exemplaribus PCI Express (LXT)

• Suffragium technologiae PCI® pretii minoris, congruens cum specificatione 33 MHz, 32 et 64 bit.

• Segmenta DSP48A1 efficacia

• Arithmetica et processus signorum summae efficacitatis

• Multiplicator celer 18 x 18 et accumulator 48-bit

• Capacitas canalium et cascadarum

• Praeadditio ad applicationem filtri adiuvandam

• Bloci Moderatoris Memoriae Integrati

• DDR, DDR2, DDR3, et LPDDR sustinentur

• Velocitates datorum usque ad 800 Mb/s (12.8 Gb/s maxima latitudo transmissionis)

• Structura bus multiportuum cum FIFO independente ad difficultates temporis designandi minuendas

• Abundantes opes logicae cum aucta capacitate logica

• Registrum translationis vel RAM distributam (facultativum) sustinet

• LUTs sex input efficaces efficientiam augent et potentiam minuerunt

• LUT cum bistabilibus duabus ad applicationes centratas in canalibus (vel canalibus)

• Memoria RAM fragmentorum cum lata granularitate

• RAM celeris cum inscriptione per bytes (vel fortasse: celeris)

• Bloci 18 Kb qui ad libitum programmari possunt ut duo separati 9 Kb RAM block

• Tegula Administrationis Horologii (CMT) ad augendam efficaciam

• Sonitus parvus, horologium flexibile

• Rectores Horologii Digitalis (RCD) obliquitatem horologii et distortionem cycli officii eliminant.

• Circuitus Phase-Locked (PLLs) pro horologio parvo tremore

• Synthesis frequentiae cum multiplicatione, divisione, et mutatione phasis simul

• Sedecim retia horologica globalia parvae inclinationis

• Configuratio simplicior, normas sumptuum humilium sustinet

• Configuratio autodetectionis duarum clavorum

• Latum SPI tertiae partis (usque ad x4) et NOR flash subsidium

• Xilinx Platform Flash dives functionibus cum JTAG

• MultiBoot subsidium pro renovatione remota cum multis fluminibus bit, utens protectione watchdog

• Securitas aucta ad designationem protegendam

• Identificator unicus ADN instrumenti ad authenticationem designationis

• Encryptio AES bitstream in maioribus machinis

• Processus integratus celerior cum processore molli MicroBlaze™ amplificato et pretio vili

• Designia IP et referentialis in industria praestantissima