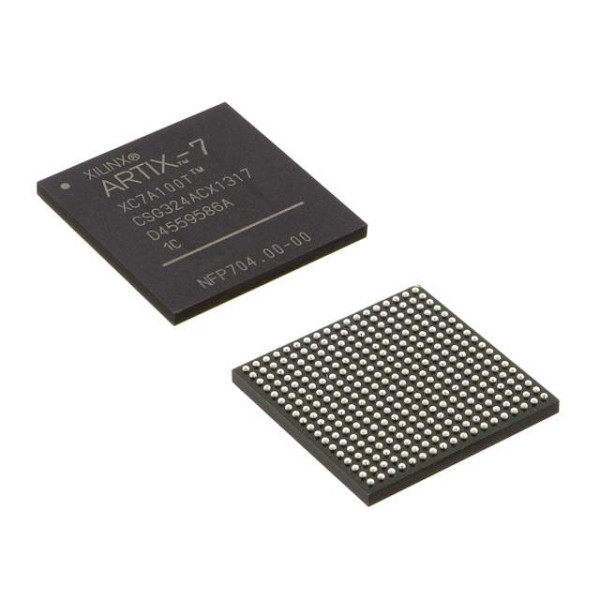

XC7A50T-2CSG324I FPGA – Series Portarum Programmabiles in Campo XC7A50T-2CSG324I

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Xilinx |

| Categoria Producti: | FPGA - Series Portarum Programmabiles in Campo |

| Series: | XC7A50T |

| Numerus Elementorum Logicorum: | 52160 LE |

| Numerus I/O: | 210 I/O |

| Tensio Alimentaria - Minimum: | 0.95 V |

| Tensio Alimentaria - Maxima: | 1.05 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | +100°C |

| Frequentia Datorum: | - |

| Numerus Transceptorum: | - |

| Modus Montandi: | SMD/SMT |

| Sarcina / Capsa: | CSBGA-324 |

| Marca: | Xilinx |

| Memoria RAM distributa: | 600 kbit |

| Memoria RAM Integrata - EBR: | 2700 kbit |

| Humoribus Sensibilis: | Ita |

| Numerus Sectorum Ordines Logici - LAB: | 4075 LABORATORIUM |

| Tensio Alimentationis Operativae: | 1 V |

| Typus Producti: | FPGA - Series Portarum Programmabiles in Campo |

| Quantitas Sarcinae Fabricae: | 1 |

| Subcategoria: | Circuiti Integrati Logicae Programmabiles |

| Nomen Mercatorium: | Artix |

| Pondus Unitarium: | Uncia una |

♠ Series FPGA Xilinx® 7 quattuor familias FPGA comprehendit, quae totam seriem requisitorum systematis amplectuntur, ab applicationibus vilibus, formae parvae, sumptibus sensibilibus, voluminis magni ad latitudinem connectivitatis, capacitatem logicam, et facultatem processus signorum summae qualitatis pro applicationibus summae perfunctionis difficillimis.

FPGA seriei 7 Xilinx® quattuor familias FPGA comprehendunt, quae totam seriem requisitorum systematis tractant, a pretiis humilibus, formae parvae, sumptibus sensibilibus, magni voluminis applicationibus ad latitudinem connectivitatis, capacitatem logicam, et facultatem processus signorum altissimi ordinis pro applicationibus summae efficaciae difficillimis. FPGA seriei 7 haec includunt:

• Familia Spartan®-7: Ad sumptum vile, minimam potentiam, et magnam efficaciam I/O optimizata. Praesto in involucro vili, formae factoris minimae, ad vestigium PCB minimum.

• Familia Artix®-7: Optimizata ad applicationes parvae potentiae quae transceptores seriales et DSP altum et logicum throughput requirunt. Minimum sumptum totalem materiae praebet ad applicationes altae productionis et sumptibus sensibiles.

• Familia Kintex®-7: Ad optimam rationem pretii et effectus optimizata cum duplo incremento comparata cum generatione priore, novam classem FPGArum efficiens.

• Familia Virtex®-7: Ad summam systematis efficaciam et capacitatem optimizata cum duplo incremento efficaciae. Instrumenta maximae capacitatis per technologiam interconnectionis silicii stratificati (SSI) efficiuntur.

In technologia processus portae metallicae summae artis, altae efficacitatis, humilis potentiae (HPL), 28 nm, et portae metallicae altae k (HKMG) constructa, FPGA seriei 7 augmentum incomparabile in efficacia systematis permittunt cum 2.9 Tb/s latitudinis transmissionis I/O, capacitate 2 millionum cellularum logicarum, et DSP 5.3 TMAC/s, dum 50% minus potentiae quam machinae generationis prioris consumunt, ut alternativam plene programmabilem ASSP et ASIC offerant.

• Logica FPGA provecta et summae efficacitatis, in vera technologia tabulae inquisitoriae (LUT) sex inputuum fundata, ut memoria distributa configurabilis.

• Memoria RAM biportus 36 Kb cum logica FIFO inclusa ad conservationem datorum in chip.

• Technologia SelectIO™ summae efficacitatis cum auxilio interfacierum DDR3 usque ad 1866 Mb/s.

• Nexus serialis celerrimus cum transceptoribus multi-gigabit inclusis ab 600 Mb/s ad maximas celeritates 6.6 Gb/s usque ad 28.05 Gb/s, modum specialem parvae potentiae offerens, pro interfaciebus inter chips aptatum.

• Interfacies analogica ab usore configurabilis (XADC), conversores analogico-digitales duos 12-bit 1MSPS cum sensoribus thermalibus et alimentationis in chip incorporans.

• Sectiones DSP cum multiplicatore 25 x 18, accumulatore 48-bit, et prae-addendo ad filtrationem magnae efficacitatis, inclusa filtratione coefficientium symmetrica optimizata.

• Potentes tegulae administrationis horologii (CMT), coniungentes partes ansae phase-clausatae (PLL) et administratoris horologii modi mixti (MMCM) ad magnam praecisionem et trepidationem parvam.

• Processum integratum celeriter cum processore MicroBlaze™ dispone.

• Pars integrata pro PCI Express® (PCIe), usque ad x8 portuum terminalium et radicum Gen3 designis.

• Ampla varietas optionum configurationis, inter quas subsidium memoriae vulgaris, encryptionem AES 256-bit cum authenticatione HMAC/SHA-256, et detectionem et correctionem SEU inclusam.

• Involucrum flip-chip vilis pretii, filis coniunctum, sine matrice, et flip-chip altae integritatis signalis, facilem migrationem inter sodales familiae in eodem involucro praebens. Omnes involucri sine plumbo praesto sunt, et involucri selecti cum optione plumbi.

• Ad summam efficaciam et minimam potentiam designatum cum 28 nm, HKMG, processu HPL, technologia processus tensionis nuclei 1.0V et optione tensionis nuclei 0.9V ad potentiam etiam minorem.