STM32H750IBK6 ARM Microcontrolers - MCU summus perficientur & DSP DP-FPU, Arm Cortex-M7 MCU 128Kbytes de Flash 1MB RAM, 480

Product Description

| Productum attributum | Precium attributum |

| Fabrica: | STMicroelectronics |

| Product Category: | ARM Microcontrollers - MCU |

| RoHS: | Singula |

| Series: | STM32H7 |

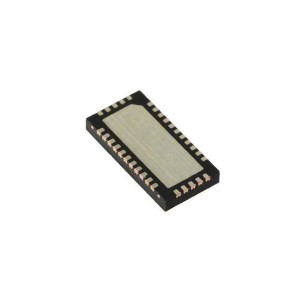

| Adscendens Style: | SMD/SMT |

| Sarcina / Causa: | UFBGA-176 |

| Core: | ARM Cortex M7 |

| Programma Memoria Location: | 128 kB |

| Data Bus Latitudo: | 32 bit |

| ADC Consilium: | 3 x 16 bit |

| Maximum Horologium Frequency: | 480 MHz |

| Numerus I / Os: | 140 I/O |

| Data Ram Size: | 1 MB |

| Supple intentione - Min: | 1.62 V |

| Supple intentione - Max: | 3.6 V |

| Minimum Operating Temperature: | - 40 C |

| Maximum Operating Temperature: | + 85 C |

| Packaging: | Tray |

| Notam: | STMicroelectronics |

| DAC Resolutio: | 12 bit |

| Data RAM Type: | aries |

| I/O intentione: | 1.62 V ad 3.6 V |

| Interface Type: | CAN, I2C, SAI, SDI, SPI, USART, USB |

| Humor Sensitivus: | Ita |

| Numerus ADC canales: | 36 Channel |

| Productum: | MCU+FPU |

| Product Type: | ARM Microcontrollers - MCU |

| Programma Memoria Type: | Flash |

| Factory Pack Quantity: | 1008 |

| Subcategoria: | Microcontrollers - MCU |

| Nomen: | STM32 |

| Watchdog Timers: | Watchdog Timer, Windowed |

| Unitas pondus: | 111 mg |

32-bit Arm® Cortex®-M7 480MHz MCUs, 128 Kbyte Flash, 1 Mbyte RAM, 46 com.et Analog interfaces, crypto

STM32H750xB machinis innituntur summus perficientur Arm® Cortex®-M7 32-bit nucleus RISC operans usque ad 480 MHz.Cortex® -M7 nucleus notat punctum fluitantis unitatis (FPU) quae Arm® praecisionem duplicem (IEEE 754 obsecundantem) sustinet et una praecisio notitiarum processus notitiarum et generum datorum.STM32H750xB machinis plenam seriem mandatorum DSP sustinent et unitas tutelae memoriae (MPU) ad securitatem applicationem augendam.

STM32H750xB cogitationes memoriae infixae cum memoria Flash incorporandi 128 Kbytes, usque ad 1 Mbyte RAM (including 192 Kbytes de TCM RAM, usque ad 864 Kbytes usoris SRAM et 4 Kbytes de tergum SRAM), tum ampla ampliatio aucta I/Os et periphericis cum APB busibus, AHB busibus, 2x32-bis multi- bus matricis AHB connexis et multi- strati AXI internexi accessum memoriam internam et externam sustinentes.

Omnes machinae tres ADCs, duo DACs, duo comparatores potentiae ultra-humilis offerunt, potentia humilis RTC, summus consulto timoris, 12 propositi generalis 16-bit timers, duo PWM timers pro potestate motoria, quinque potentia humilis timentes. , numerus vero temere generans (RNG) et cellam accelerationis cryptographicae.Instrumenta quattuor filtra digitales ad sigma-delta modulatores externas adiuvant (DFSDM).Ipsi etiam vexillum interfaciunt ac communicationis progressum interfaciunt.

Includes ST state-of-arte patented technologia

Core

• 32-bit Arm® Cortex®-M7 nucleus cum duplici praecisione FPU et L1 cache: 16 Kbytes notitiarum et 16 kbytes cella instructionis;frequentia usque ad 480 MHz, MPU, 1027 DMIPS/ 2.14 DMIPS/MHz (Dhrystone 2.1), et instructiones DSP

Memoriae

• 128 Kbytes de Mico memoria

• 1 Mbyte de RAM: 192 Kbytes de TCM RAM (inc. 64 Kbytes de ITC RAM + 128 Kbytes de DTCM RAM pro tempore criticae consuetudines), 864 Kbytes usoris SRAM, et 4 Kbytes de SRAM in Tergum dominicum.

• Dual modus Quad-SPI memoria interfaciei accurrit ad 133 MHz

• Flexibile memoriae externae moderatoris cum usque ad 32 frenum data bus: - SRAM, PSRAM, NEC Mico memoria ad 133 MHz in modo synchrono - SDRAM/LPSDR SDRAM - 8/16-bit NAND memorias Flash.

• CRC unitas calculum

Securitas

• ROP, PC-ROP, activum sollicitare, firmam firmare upgrade subsidium, securam accessum modum

General-proposito initus/outputs

• Usque ad CLXVIII I / O portus facultatem adjicias

Reset et imperium procuratio

• 3 ditiones potentiae separatae quae sine clock-gato vel switchedi esse possunt;

- D1: summus perficientur capabilities

- D2: communicationis peripherales et timers

- D3: reset / horologium imperium / potentia procuratio

• 1.62 ad 3.6 V applicationis copiam et I/Os

• POR, PDR, PVD et BOR

• USB potentiae dedicatae 3.3 V ordinator internus embedendi ad supplendam internam PHYs

• Regulator Embedded (LDO) configurable scalable output supplere digitalis circuitry

• intentione scalis in currendo et Sistere modus (configurable VI septa)

• Tergum moderator (~0.9 V)

• Voltage reference for Analog periphericum/VREF+

• Low-power modes: Somnus, Siste, Standby et VBAT sustinentes altilium præcipientes

Humilis potentia consummatio

• VBAT altilium operandi modus cum præcipiens facultatem

• CPU and domain power state vigilanting pins

• 2.95 µA in Sto modo (Tergum SRAM OFF, RTC/LSE ON)

Horologium procuratio

• VBAT altilium operandi modus cum præcipiens facultatem

• CPU and domain power state vigilanting pins

• 2.95 µA in Sto modo (Tergum SRAM OFF, RTC/LSE ON)

Interconnect matrix

• 3 bus matrices (1 AXI et 2 AHB)

• Pontes (5× AHB2-APB, 2× AXI2-AHB)

IV DMA moderatoris exonerare CPU

• 1× summus celeritas dominus directus memoriae obvius moderatoris (MDMA) cum indice coniuncto auxilio

• 2× dual-portus DMAs cum FIFO

• 1× basic DMA cum iter itineris petitionem capabilities

Ad XXXV communicationis peripherals

• 4× I2Cs FM+ interfaces (SMBus/PMBus)

• 4× USARTs/4x UARTs (ISO7816 interface, LIN, IrDA, usque ad 12.5 Mbit/s) et 1x LPUART.

• 6× SPIs, 3 cum muxed duplex I2S accurationis genus audii per PLL internum seu externum horologium, 1x I2S in LP domain (usque ad 150 MHz)

• 4x SAIs (Vide audio interface)

• SPDIFRX interface

• SWPMI unum filum protocol dominus I / F *

• MDIO Servus interface

• 2× SD/SDIO/MMC interfaces (usque ad 125 MHz)

• 2× moderatores POTEST: 2 cum FD Can, 1 cum tempore Can (TT-CAN)

• 2× USB OTG interfacies (1FS, 1HS/FS) cristallina solutionis minus cum LPM et BCD.

• Aer MAC interface cum DMA controller

• HDMI-CEC • 8- ad 14 frenum camerae instrumenti (usque ad 80 MHz)

XI Analog peripherals

• 3× ADCs cum 16-bit max.resolutio (usque ad XXXVI canales, ad 3.6 MSPS)

• 1× temperatus sensorem

• 2× 12-bit D/A conversis (1 MHz)

• 2× ultra-humilis potentia comparatorum

• 2× ampliatores perficiendi (Sed 7.3 MHz)

• 1× Filtra digitalis pro sigma della modulator (DFSDM) cum canalibus 8/4 filters

Graphics

• LCD-TFT moderatoris ad XGA resolutio

• Chrom-ART hardware graphical Accelerator (DMA2D) ad redigendum CPU onus

• Hardware JPEG Codec

Ad XXII timers et canes

• 1× summus consultum timor (2.1 ns max resolutio)

• 2× 32-bit timers usque ad 4 IC/OC/PWM vel pulsus calculo et quadratura (incrementalis) encoder initus (usque ad 240 MHz)

• 2× 16-bit timers imperium motoris provectum (usque ad 240 MHz)

• 10× 16-bit generalis propositi timers (usque ad 240 MHz)

• 5× 16-bit potentia humilis timers (usque ad 240 MHz)

• 2× canes (solutae et fenestrae)

• 1× SysTick timer

• RTC cum sub-secundo accurate et hardware calendarium

Cryptographica acceleratio

128, 192, 256, TDES;

• HASH (MD5, SHA-I, SHA-2), HMAC

• Verum temere numerus generantium

Debug modus

• SWD & JTAG interfaces

• 4-Kbyte embedded Trace Buffer