TMS320C6674ACYPA Multicore Fix/Float Pt Dig Sig Proc

Product Description

| Productum attributum | Precium attributum |

| Fabrica: | Texas Instrumenta |

| Product Category: | Digital Signum Processores & Moderatores - DSP, DSC |

| Productum: | DSPs |

| Series: | TMS320C6674 |

| Adscendens Style: | SMD/SMT |

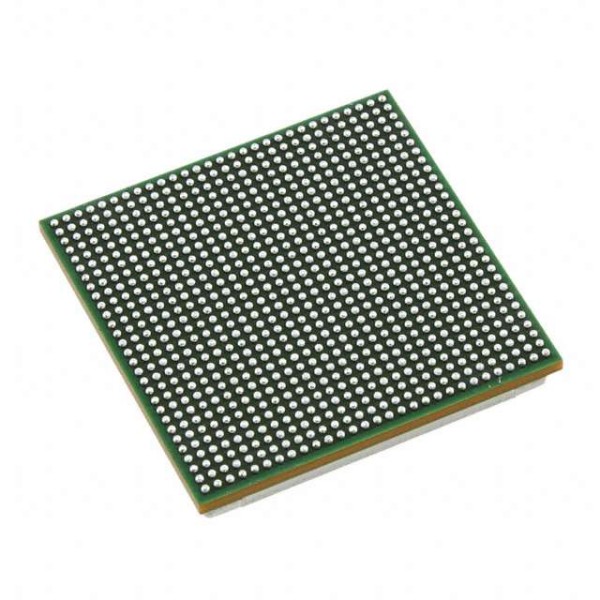

| Sarcina / Case: | FCBGA-841 |

| Core: | C66x |

| Numerus Cores: | 4 Core |

| Maximum Horologium Frequency: | 1 GHz, 1.25 GHz |

| L1 Cache Instructio Memoria: | 4 x 32 kB |

| L1 Cache Data Memoria: | 4 x 32 kB |

| Programma Memoria Location: | - |

| Data Ram Size: | - |

| Supple intentione operating: | 900 mV ad 1.1 V |

| Minimum Operating Temperature: | - 40 C |

| Maximum Operating Temperature: | + 100 C |

| Packaging: | Tray |

| Notam: | Texas Instrumenta |

| Data Bus Latitudo: | 8 bit/16 bit/32 bit |

| Instructio Type: | Fixum / fluctuetur |

| MMACS: | 160000 MMACS |

| Humor Sensitivus: | Ita |

| Numerus I / Os: | 16 I/O |

| Numerus Timers / Calculis: | 12 Timer |

| Product Type: | DSP - Digital signum Processors & Controllers |

| Factory Pack Quantity: | 44 |

| Subcategoria: | Embedded Processors & Controllers |

| Supple intentione - Max: | 1.1 V |

| Supple intentione - Min: | 900 mV |

| Unitas pondus: | 0.17336 oz |

Multicore certa et fluctuetur-Point Digital signum Processor

TMS320C6674 DSP maxima opera fixa est / punctum DSP fluitantis quod ex architectura multicore TI in KeyStone fundatur.Incorporandi novum et innovative C66x DSP nucleum, haec fabrica currere potest ad nucleum celeritatis usque ad 1.25 GHz.In tincidunt amplis applicationibus, ut systemata missioni-critica, imaginatio medicinae, experimento et automatione, aliisque applicationibus altae operationis requirunt, TI'S TMS320C6674 DSP 5 GHz cumulativum DSP offert et suggestum efficax et facile dat. uteris.Praeterea plene retrorsum compatible cum omni exsistente C6000 domo fixa et fluctuetur punctum DSPs.

TI'S KeyStone architectura praebet programmabilem suggestum variis subsystematibus (C66x coros, memoriae subsystem, periphericis et acceleratoribus) et utitur pluribus componentibus et technicis rationibus ad maximizandum intra-machinam et inter-machinam communicationis, quae varias facultates DSP efficienter et compagem operandi permittit. .Integrae huic architecturae partes praecipuae sunt ut Multicore Navigator qui dat procurationem efficientis inter varias machinas compositas.TeraNet est fabricae transiens non-obclusio ut motus celeritatis et contentionis liberorum internorum notitiarum possit.Multicore communis memoria moderatoris aditum ad memoriam communem et externam permittit directe sine e facultate switch fabricae trahens.

• Quattuor TMS320C66x™ DSP Core Subsystems (C66x CorePacs), Quisque cum

- 1.0 GHz vel 1.25 GHz C66x Fixarum / Fluctuans-Point CPU Core

40 GMAC/Core pro Fixum @ 1.25 GHz

20 GFLOP/Core for Floating Point @ 1.25 GHz

- Memoria

› 32K Byte L1P Per Core

32K Byte L1D Per Core

› 512K Byte Local L2 Per Core

• Multicore Shared Memoria Controller (MSMC)

- 4096KB MSM SRAM Memoria Communes per quattuor DSP C66x CorePacs

- Memoria Protectionis Unitas utriusque MSM SRAM et DDR3_EMIF

• Multicore Navigator

- 8192 Multipurpose Hardware Queues cum Queue Manager

- fasciculum-Substructio DMA ad Nulla supra caput Transfers

• Network Coprocessor

- Packet Accelerator ope Support

› Transporto Planum IPsec, GTP-U, SCTP, PDCP

L2 User Planum PDCP (RoHC, Air Ciphering)

›1-Gbps Wire velocitate Throughput ad 1.5 MPackets Per Second

- Securitatis Accelerator Engine ope adiuvat

IPSec, SRTP, 3GPP, WiMAX Aeris mollis ac SSL/TLS Securitatis

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, NIVEUS 3G, SHA-1, SHA-2 (256-bit Hash), MD5

Ad 2.8 Gbps Encryption Volo

• Peripherals

- Quattuor vicos SRIO 2.1

1.24/2.5/3.125/5 Operatio GBaud suffulta Per Lane

subsidia Direct I/O, Nuntius Transitus

Sustinet quattuor 1×, duae 2×, unus 4×, et duae 1× + unus 2×, Link configurationes

– Plu Gen2

Unius Portus Supportantes I vel II Lancs

Sustinet ad V GBaud Per Lane

- HyperLink

subsidia connexiones ad Alia KeyStone Architectura machinae Providentes Resource Scalability

subsidia ad L Gbaud

– Gigabit Ethernet (GbE) Switch Subsystem

Duo SGMII portuum

subsidia 10/100/1000 Mbps Operatio

- 64-Bit DDR3 Interface (DDR3-1600)

8G MB Addressable Memoria Space

- 16-bit EMIF

- Duo Telecom Serial Portus (TSIP)

subsidia 1024 DS0s Per TSIP

Supports 2/4/8 Lancs at 32.768/16.384/8.192 Mbps Per Lane

- UART Interface

- I²C interface

- 16 GPIO Pins

- SPI Interface

- Semaphore amet

- Duodecim 64-bit Timers

- Tres De Chip PLLs

• Commercial Temperature:

- 0°C ad 85°C

• Calor Extensus:

– -40°C ad 100°C

• Mission-Critical Systems

• High-Perficiendi Computing Systems

• Communications

• Audio

• Vide Infrastructure

• Imaging

• Analytics

• Networking

• Media Processing

• Industrial Automation

• Automation et Processus Imperium