TMS320C6678ACYPA Processor Signationis Digitalis Multinuclearis Punti Fixi/Flotantis

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Instrumenta Texana |

| Categoria Producti: | Processores et Moderatores Signorum Digitalium - DSP, DSC |

| Productum: | DSPs |

| Series: | TMS320C6678 |

| Modus Montandi: | SMD/SMT |

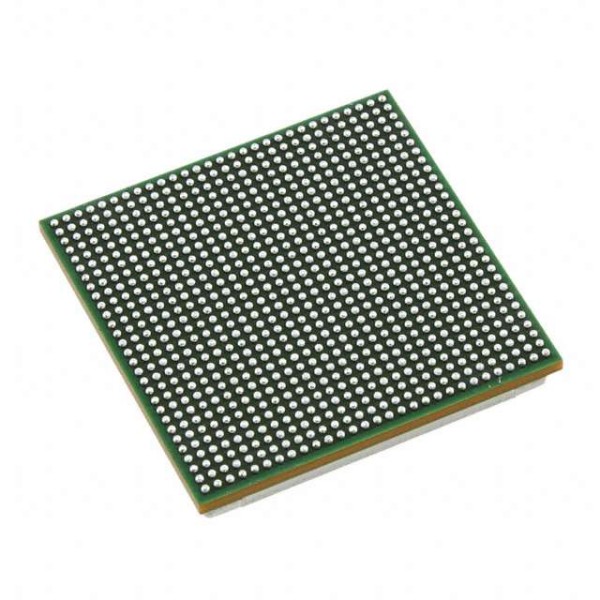

| Sarcina / Capsa: | FCBGA-841 |

| Nucleus: | C66x |

| Numerus Nucleorum: | Octo Nuclei |

| Frequentia Horologii Maxima: | 1 GHz, 1.25 GHz |

| Memoria Instructionum Cache L1: | Octo per triginta duo kilobytes |

| Memoria Datorum Cessandi L1: | Octo per triginta duo kilobytes |

| Magnitudo Memoriae Programmatis: | - |

| Magnitudo Memoriae Memoriae Datorum: | - |

| Tensio Alimentationis Operativae: | 900 mV ad 1.1 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | +100°C |

| Involucrum: | Ferculum |

| Marca: | Instrumenta Texana |

| Latitudo Bus Datorum: | Octo bit/sedecim bit/triginta duo bit |

| Typus Instructionis: | Punctum Fixum/Varians |

| MMACS: | 320000 MMACS |

| Humoribus Sensibilis: | Ita |

| Numerus I/O: | XVI I/O |

| Numerus Temporatorum/Numeratorum: | Temporarium XVI |

| Typus Producti: | DSP - Processores et Moderatores Signorum Digitalium |

| Quantitas Sarcinae Fabricae: | 44 |

| Subcategoria: | Processores et Moderatores Incorporati |

| Tensio Alimentaria - Maxima: | 1.1 V |

| Tensio Alimentaria - Minimum: | 900 mV |

| Pondus Unitarium: | 0.252724 unciae |

♠ Processor Signorum Digitalium Multinucleorum Fixorum et Computationis Fluitantis

DSP TMS320C6678 est DSP puncti fixi/fluctuantis summae efficaciae, in architectura multicore KeyStone societatis TI fundatum. Nucleo DSP novo et innovativo C66x incorporato, hoc instrumentum celeritate nuclei usque ad 1.4 GHz currere potest. Pro fabricatoribus amplae applicationum varietatis, ut systematum criticorum, imaginum medicarum, probationum et automationis, et aliarum applicationum magnam efficaciam requirentium, DSP TMS320C6678 societatis TI DSP cumulativum 11.2 GHz offert et suggestum efficit quod energiae parcum est et facile utendum. Praeterea, plene retro compatibilis est cum omnibus DSP puncti fixi et fluctuantis familiae C6000 existentibus.

Architectura KeyStone societatis TI suggestum programmabile praebet, varia subsystemata (nucleos C66x, subsystema memoriae, peripherica, et acceleratoria) integrans, et pluribus componentibus et artibus novis utitur ad communicationem intra et inter machinas amplificandam, quae permittit ut variae opes DSP efficaciter et sine intermissione operentur. Centralis huic architecturae sunt componentes clavis, ut Navigator Multicore, qui efficientem administrationem datorum inter varia elementa machinae permittit. TeraNet est structura commutationis non-obstruens, quae motum datorum internum celerem et sine contentione permittit. Moderator memoriae communis multicore accessum ad memoriam communem et externam directe sine usu ex capacitate structurae commutationis permittit.

• Octo Subsystemata Centralia DSP TMS320C66x™ (C66x CorePacs), Singula cum

– Nucleus CPU C66x Fixi/Virgae Fluitantis 1.0 GHz, 1.25 GHz, vel 1.4 GHz

› 44.8 GMAC/Nucleus pro Puncto Fixo @ 1.4 GHz

› 22.4 GFLOP/Nucleus pro Computatro Fluitante @ 1.4 GHz

– Memoria

› 32K Byte L1P per Nucleum

› 32K Byte L1D per Nucleum

› 512K Byte Localis L2 Per Nucleum

• Moderator Memoriae Communis Multinuclei (MSMC)

– Memoria SRAM MSM 4096KB ab octo DSP C66x CorePacs communicata

– Unitas Protectionis Memoriae pro MSM SRAM et DDR3_EMIF

• Navigator Multinucleus

– 8192 Filae Instrumentorum Multipropositarum cum Administratore Filarum

– DMA Fasciculis Fundatum pro Translationibus Sine Superficie

• Coprocessor Retialis

– Accelerator fasciculorum auxilium praebet pro

› Planum Transportationis IPsec, GTP-U, SCTP, PDCP

› Planum Usoris L2 PDCP (RoHC, Cifratio Aerea)

› Transmissio Filorum 1 Gbps ad 1.5 MPackets Per Secundum

– Machina Acceleratoris Securitatis Auxilium Permittit pro

› IPSec, SRTP, 3GPP, Interfacies Aerea WiMAX, et Securitas SSL/TLS

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (Computatio Divisoria 256-bit), MD5

› Celeritas Encryptionis Usque ad 2.8 Gbps

• Peripherica

– Quattuor Viae SRIO 2.1

› 1.24/2.5/3.125/5 GBaud Operatio Sustentata Per Lineam

› Sustinet Direct I/O, Nuntiorum Transmissionem

› Quattuor configurationes nexuum 1×, duas 2×, unam 4×, et duas 1× + unam 2× sustinet.

– PCIe Gen2

› Portus Singularis Unam aut Duas Vias Sustinens

› Sustinet Usque ad 5 GBaud per Lineam

– Nexus Hyperactivus

› Conexiones cum aliis instrumentis architecturae KeyStone sustinet, scalabilitatem opum praebens.

› Usque ad 50 Gbaud sustinet

– Subsystema Commutationis Gigabit Ethernet (GbE)

› Duo Portus SGMII

› Operationem 10/100/1000 Mbps sustinet

– Interfacies DDR3 64-Bit (DDR3-1600)

› Spatium Memoriae Addressabilis 8G Byte

– EMIF sedecim bitorum

– Duo Portus Seriales Telecom (TSIP)

› Sustinet 1024 DS0s per TSIP

› Sustinet 2/4/8 vias ad 32.768/16.384/8.192 Mbps per viam

– Interfacies UART

– I2

Interfacies C

– 16 clavi GPIO

– Interfacies SPI

– Modulus Semaphori

– Sedecim Temporatores 64-Bit

– Tres PLL in chip

• Temperatura Commercialis:

– 0°C ad 85°C

• Temperatura Extensa:

– -40°C ad 100°C

• Systemata Missionis Critica

• Systema Computandi Altae Perfunctionis

• Communicationes

• Audio

• Infrastructura Videorum

• Imaginatio

• Analytica

• Retia

• Processus Medialis

• Automatio Industrialis

• Automatio et Moderatio Processuum