TMS320F2812PGFA Processores et Moderatores Signorum Digitalium DSP DSC Moderator Signorum Digitalium 32-Bit cum Memoria Flash

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Instrumenta Texana |

| Categoria Producti: | Processores et Moderatores Signorum Digitalium - DSP, DSC |

| RoHS: | Detalia |

| Productum: | DSCs |

| Series: | TMS320F2812 |

| Nomen Mercatorium: | C2000 |

| Modus Montandi: | SMD/SMT |

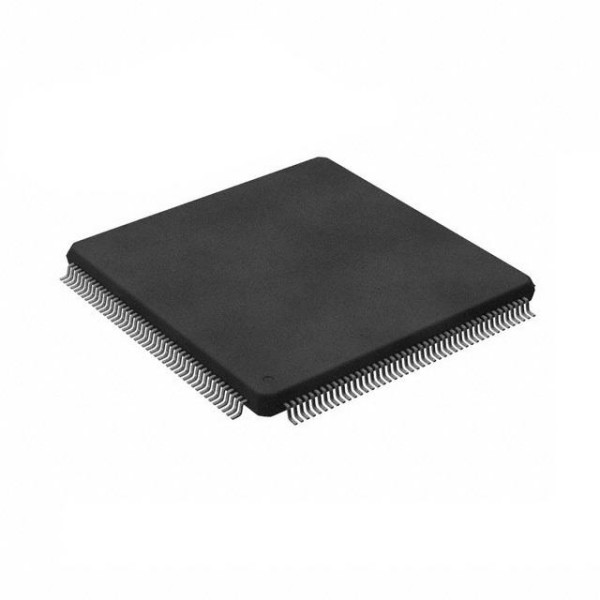

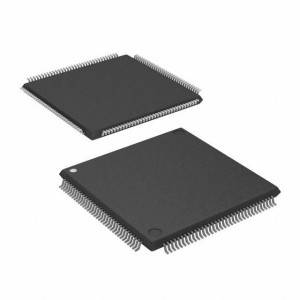

| Sarcina / Capsa: | LQFP-176 |

| Nucleus: | C28x |

| Numerus Nucleorum: | 1 Nucleus |

| Frequentia Horologii Maxima: | 150 MHz |

| Memoria Instructionum Cache L1: | - |

| Memoria Datorum Cessandi L1: | - |

| Magnitudo Memoriae Programmatis: | 256 kB |

| Magnitudo Memoriae Memoriae Datorum: | 36 kB |

| Tensio Alimentationis Operativae: | 1.9 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | + 125°C |

| Involucrum: | Ferculum |

| Resolutio ADC: | Duodecim bit |

| Marca: | Instrumenta Texana |

| Latitudo Bus Datorum: | Triginta duo bit |

| Tensio I/O: | 3.3 V |

| Typus Instructionis: | Punctum Fixum |

| Humoribus Sensibilis: | Ita |

| Typus Producti: | DSP - Processores et Moderatores Signorum Digitalium |

| Quantitas Sarcinae Fabricae: | 40 |

| Subcategoria: | Processores et Moderatores Incorporati |

| Pondus Unitarium: | 0.066886 unciae |

• Technologia CMOS statica summae efficaciae

– 150 MHz (tempus cycli 6.67-ns)

– Parvae potentiae (nucleus 1.8-V ad 135 MHz,Nucleus 1.9-V ad 150 MHz, designatio 3.3-VI/O

• JTAG limites perscrutationis sustinet

– Norma IEEE 1149.1-1990 Norma IEEEExperimentum Portus Accessus et Scrutatio FinisArchitectura

• CPU 32-bit summae efficacitatis (TMS320C28x)

– Operationes MAC 16 × 16 et 32 × 32

– MAC duplex 16 × 16

– Architectura autobus Harvardiana

– Operationes atomicae

– Celeris responsio ad interruptiones et processus

– exemplar programmandi memoriae unificatae

– 4M extensionem inscriptionis programmatis/datorum linearis

– Efficax in codice (in C/C++ et Assembly)

– Codex fons processoris TMS320F24x/LF240xcongruens

• Memoria in chip

– Usque ad 128K × 16 imagines fulgurantes(Quattuor sectores 8K × 16 et sex 16K × 16)

– 1K × 16 OTP ROM

– L0 et L1: duo segmenta 4K × 16 singula SingleAccess RAM (SARAM)

– H0: 1 frustum 8K × 16 SARAM

– M0 et M1: duo segmenta 1K × 16 singula SARAM

• ROM Initiandi (4K × 16)

– Cum modis programmatis incipiendi

– Tabulae mathematicae ordinariae

• Interfacies externa (F2812)

– Memoria totalis plus quam 1M × 16

– Status exspectationis programmabiles

– Tempus stroboscopicum legendi/scribendi programmabile

– Tres selectiones singularum fragmentorum

• Endianitas: Little endian

• Horologium et systema moderari

– Oscillator in chip

– Modulus temporis custodiendi

• Tres interruptiones externae

• Quadrum Expansionis Interruptionis Periphericae (PIE) quod45 interruptiones periphericas sustinet

• Tria tempora CPU 32-bit

• Clavis/sera securitatis 128-bit

– Memoriam memoriae/OTP et SARAM L0/L1 protegit.

– Ingeniariam inversam firmware impedit

• Peripherica moderationis motoris

– Duo Curatores Eventuum (EVA, EVB)

– Compatibilis cum machinis 240xA

• Peripherica portus serialis

– Interfacies Peripherica Serialis (SPI)

– Duae Interfacies Communicationis Serialis (SCI),UART normae

– Rete Areae Moderatoris Augmentata (eCAN)

– Portus Serialis Multicanalis Bufferatus (McBSP)

• ADC 12-bit, 16 canales

– Multiplexor inputus canalium 2 × 8

– Duo Sample-and-Hold

– Conversiones singulares/simultaneae

– Celeris conversio celeritas: 80 ns/12.5 MSPS

• Usque ad 56 paxilli I/O Usus Generalis (GPIO)

• Aemulationis facultates provectiores

– Functiones analyticae et punctorum interruptionis

– Depuratio temporis realis per apparatum

• Instrumenta progressionis includunt

– compilator/assemblator/coniunctor ANSI C/C++

– Code Composer Studio™ IDE

– DSP/BIOS™

– Moderatores JTAG scansionis

• Norma IEEE 1149.1-1990 Norma IEEEExperimentum Portus Accessus et Scrutatio FinisArchitectura

• Modi parvae potentiae et conservatio potentiae

– Modi ODIOSUS, EXSPECTUS, CONSTITUTIO sustinentur

– Horologia peripherica singula inactivare

• Optiones fasciculorum

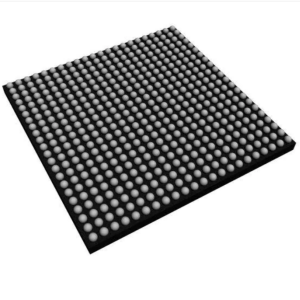

– MicroStar BGA™ 179-globorum cum memoria externainterfacies (GHH, ZHH) (F2812)

– Quadruplae formae humilis planae (LQFP) 176-aciculorum cuminterfacies memoriae externae (PGF) (F2812)

– LQFP 128-clavorum sine memoria externainterfacies (PBK) (F2810, F2811)

• Optiones temperaturae

– A: –40°C ad 85°C (GHH, ZHH, PGF, PBK)

– S: –40°C ad 125°C (GHH, ZHH, PGF, PBK)

– Q: –40°C ad 125°C (PGF, PBK)(Qualificatio AEC-Q100 pro autocinetis)

applicationes)

• Systema Subsidii Aurigae Provectum (ADAS)

• Automatio aedificiorum

• Locus venditionis electronicus

• Vehiculum Electricum/Vehiculum Electricum Hybridum (EV/HEV)machina potentiae

• Automatio officinarum

• Infrastructura retiaria

• Vectura industrialis

• Medicina, cura sanitatis, et exercitatio corporis

• Impulsus motorii

• Traditio potentiae

• Infrastructura telecommunicationis

• Examen et mensura