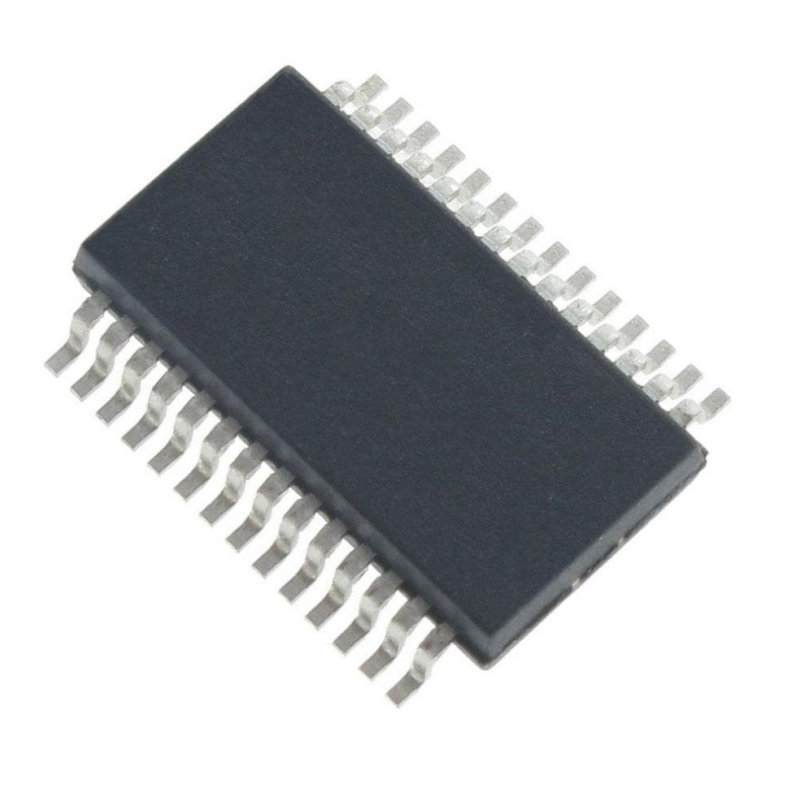

PIC18F27Q84-I/SS Microcontrollores 8-bit MCU CAN-FD Memoria Flash 128KB RAM 13KB

♠ Descriptio Producti

| Attributum Producti | Valor Attributi |

| Fabricator: | Microcip |

| Categoria Producti: | Microcontrollores octo-bit - MCU |

| RoHS: | Detalia |

| Series: | PIC18F27Q84 |

| Modus Montandi: | SMD/SMT |

| Sarcina / Capsa: | SSOP-28 |

| Nucleus: | PIC18 |

| Magnitudo Memoriae Programmatis: | 128 kB |

| Latitudo Bus Datorum: | Octo bit |

| Resolutio ADC: | Duodecim bit |

| Frequentia Horologii Maxima: | 64 MHz |

| Numerus I/O: | 25 I/O |

| Magnitudo Memoriae Memoriae Datorum: | 12.5 kB |

| Tensio Alimentaria - Minimum: | 1.8 V |

| Tensio Alimentaria - Maxima: | 5.5 V |

| Temperatura Operativa Minima: | - 40°C |

| Temperatura Maxima Operativa: | +85°C |

| Involucrum: | Tubus |

| Marca: | Technologia Microcip / Atmel |

| Humoribus Sensibilis: | Ita |

| Productum: | MCU |

| Typus Producti: | Microcontrollores octo-bit - MCU |

| Quantitas Sarcinae Fabricae: | 47 |

| Subcategoria: | Microcontrollores - MCU |

| Nomen Mercatorium: | PIC |

♠ Microcontroller 28/40/44/48-clavorum, parvae potentiae, altae efficaciae cum technologia XLP

Familia microcontrollorum PIC18-Q84 praesto est in machinis 28/40/44/48-clavorum ad multas applicationes autocineticas et industriales. Multae periphericae communicationis in familia productorum inventae, ut Rete Areae Controllorum (CAN), Interfacies Peripherica Serialis (SPI), Circuitus Interintegratus (I2C), duo Transmissores Receptores Asynchroni Universales (UART), amplam varietatem protocollorum communicationis filariorum et sine filo (per modulos externos) ad applicationes intelligentes tractare possunt. Cum facultatibus integrationis Periphericarum Independentium Nuclei (CIP) coniuncta, haec facultas functiones ad applicationes moderationis motoris, alimentationis electricae, sensoris, signorum et interfaciei usoris permittit. Praeterea, haec familia includit Convertorem Analogicum-Digitalem (ADC) 12-bit cum extensionibus Computationis et Commutationis Contextus ad analysin signorum automatariam ad complexitatem applicationis reducendam.

• Architectura RISC a Compilatore C Optimizata

• Celeritas Operandi:

– DC – 64 MHz horologii ingressus

– Cyclus instructionum minimus 62.5 ns

• Octo Moderatores Accessus Memoriae Directi (DMA):

– Translationes datorum ad spatia SFR/GPR ex memoria programmatis (Programmate Flash Memory), ex memoria datorum EEPROM, vel ex SFR/GPRspatia

– Magnitudines fontis et destinationis ab usore programmabiles

– Translationes datorum per apparatum et programmata incitatae

• Facultas Interruptionis Vectoralis:

– Prioritas alta/humila eligenda

– Latentia interruptionis trium cyclorum instructionum fixa

– Inscriptio basis tabulae vectoris programmabilis

– Retro compatibilis cum prioribus facultatibus interruptionis

• Acervus Instrumentorum Profundus 128 Graduum

• Restitutio Potestatis Accendentis Humilis Currentis (POR)

• Temporarium Actionis Configurabile (PWRT)

• Restitutio post interruptionem tensionis (BOR)

• Optio BOR Potentiae Parvae (LPBOR)

• Temporis Custodiae Fenestratus (WWDT):

– Restitutio Custodis (watchdog) in intervallo nimis longo vel nimis brevi inter eventus purgationis watchdog

– Selectio praescalatoris variabilis

– Selectio magnitudinis fenestrae variabilis