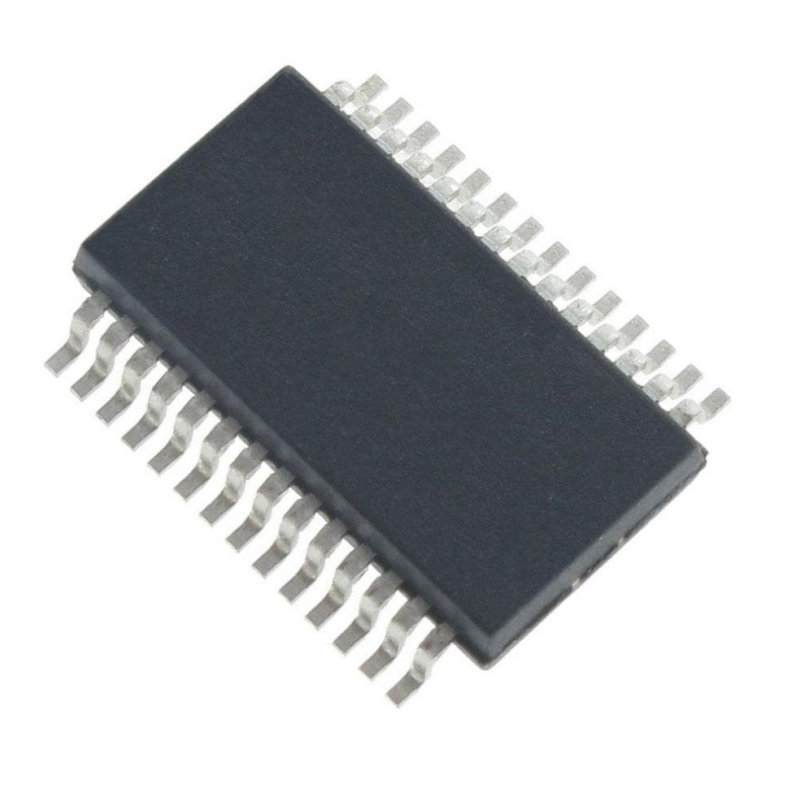

PIC18F27Q84-I/SS 8bit Microcontrollers MCU CAN-FD 128KB Flash 13KB RAM

Product Description

| Productum attributum | Precium attributum |

| Fabrica: | Microchip |

| Product Category: | 8-bit Microcontrollers - MCU |

| RoHS: | Singula |

| Series: | PIC18F27Q84 |

| Adscendens Style: | SMD/SMT |

| Sarcina / Case: | SSOP-28 |

| Core: | PIC18 |

| Programma Memoria Location: | 128 kB |

| Data Bus Latitudo: | 8 bit |

| ADC Consilium: | 12 bit |

| Maximum Horologium Frequency: | 64 MHz |

| Numerus I / Os: | 25 I/O |

| Data Ram Size: | 12.5 kB |

| Supple intentione - Min: | 1.8 V |

| Supple intentione - Max: | 5.5 V |

| Minimum Operating Temperature: | - 40 C |

| Maximum Operating Temperature: | + 85 C |

| Packaging: | Tubus |

| Notam: | Microchip Technology / Atmel |

| Humor Sensitivus: | Ita |

| Productum: | MCU |

| Product Type: | 8-bit Microcontrollers - MCU |

| Factory Pack Quantity: | 47 |

| Subcategoria: | Microcontrollers - MCU |

| Nomen: | PIC |

♠ 28/40/44/48-pin, Low-Power, High-Perficiendi Microcontroller apud XLP Technology

PIC18-Q84 microcontroller familia in 28/40/44/48 clavorum machinas praesto est multis applicationibus autocinetis et industrialibus.Multi peripherales communicationis in familia producti inventi sunt, ut Area Network Controller (CAN), Serial interface periphericis (SPI), Circuitus inter-integratus (I2C), duo Receptori Universalis Asynchroni Transmitters (UARTs), amplis wired tractare possunt. ac wireless (externis modulis utens) protocolla communicationis pro applicationibus intelligentiis.Facultates integrationis Core Independentium (CIPs) deducta, haec capacitas munera dat ad imperium motorum, vim copiam, sensorem, signum et applicationes interfaciei utentis.Accedit, haec familia in duodecim frenum Analog-ad-Digital Converter (ADC) cum Computatione et Contextu extensiones switching pro automated signo analysi ad redigendum multiplicitatem applicationis.

• C Compiler Optimised RISC Architecture

• operating velocitate

– DC - 64 MHz horologium input

- 62.5 ns minimum instructionis cycli

• octo Direct Memoria Access (DMA) Moderatores:

- Data translationes ad SFR/GPR spatia ab utraque Program Mico Memoria, Data EEPROM vel SFR/GPRspatia

- User-programma fonte et destinatione magnitudinum

- Hardware et software utitur notitia translationes

• Vectored Facultatem adjicias:

- Selectable princeps / prius humilis

- Fixum interrumpere latency trium disciplinam circuitus

- Programmable vector mensam base inscriptio

- Retrorsum compatible cum priorem facultatem adjicias

• 128-Level Deep Hardware Stack

• Low-Current Power-de Reddere (POR)

• Configurable Power-sursum Vicis (PWRT)

• Brown-e Reset (BOR)

• Low-Power BOR (LPBOR) Option

• Windowed Watchdog Timer (WWDT);

- Watchdog Reset in nimium longum vel brevior intervallum inter vigilans patet eventus

- Variabilis prescaler lectio

- Variabilis fenestra magnitudinis lectio